#### エーナエロリ

# Introduction to Binary System and Codes; Digital Systems:

- Digital systems can be sneber to the present technology parial as digital age.

- Digital aystery are used in communication, business Evansactions, traffic control, internet and so on.

- we have digital telephones, digital televisions, digital versatile discs, digital cameras, & also digital computors

- These devices have graphical user intertaces (GUIs), which enable them to execute commands that appear to the user to be simple.

- It involves in precise execution of sequence of complex internal instructions

- The mast striking properly of digital computer is its generality.

- It can tollow a sequence of instructions, called a program, that operates on a given data.

- one characteristic of digital system is their ability to represent and manipulate discrete elements of intermation.

- Any set that is nestricted to a finite number of elements ontain disconete information.

89: 10 decimal digits.

26 letters at alphabet.

52 playing cools.

. 64 squares to a chess board,

- In this case, the discrete elements were the digits.

- From, this the term digital computer emerged.

- A digital system is simply one. Hat specieves input, processes (a) controls activity, and outputs information in a disconete (a) noncontinuous manner.

- The intermation may be "encoded (or)

it can be in the tramiliar back to number cyclem or in some other number cyclem, such as back 2 (binary)

- Digital design is the application of set of rules and techniques tor developing degital circuits and subsystems to create a solution for some problem.

Attended to the religion linked to prompt good the same of

described adjust the receiving the restly as where it is the

that peralle or a green data.

on home with a light plan is then it has it is

whenite & though stoops oldgren by the go

the state of the state of the day got

Sodaly of the same

root motor of the

the triber .

in your of a charact.

the it all something

- Discorete elements of intermation one superesented in digital system by physical quantities called agrals.

- Electrical cignals such as voltage and current are most common.

- Electronic (circuits) devices called transistery predominate in the circuitry that implement these signals.

- The agnaly in dielectronic digital systems we just two discorde values and one thousand to be binary.

- A binary digit called a bit, has two values: 0 and 1

- Discorete elements of intermation are prepresented with group of bits alled binary rades.

- Eq: Decimal digits a to 9 are superesented with town bits.

- the general-purpose digital computer is the best-known example of digital system.

- The major poals of a computer are a memory unit, a central processing unit, and input-output units.

- A digital computer is a powerful instrument that an pertorm not only withmetic computations, but also logical operations.

- In addition, it can be programmed to make decisions based on internal and external commands.

- A digital gytern is an interconnection of digital modules.

- To understand the operation of each digital module, it is necessary to have a basic knowledge of digital circuits and their logical function.

- 1 min trad in ligital design methodology; the cut of HOL

- An HDL gesembles a programming language and is suitable for describing digital circuits in textual form.

- It is used to simulate a digital system to vonity its appointm betore hardware is built.

#### the seal of the season of the seal of the Binary Numbery:

- A decimal number such as 7,392 suppresents a quantity equals to 7000+ 7 thousands + 3 hundred + 9 tens + 2 units. to be well well as a second

- The thousands, hundreds, etc. are powers of 10 implied by position of the coefficients (symbols) in the number. 5t can be expressed of commend in last

- In general, a number with a decimal point is siepresented by a reries of coefficients.

- The coefficients of are any of the adigits (0,1,2,3,...,9), and the subscript value i gives the place value and, hence, the power to by which the octobiciont must be multiplied.

- Thus, a decimal number can be expressed of

10° as + 10° ay + 10° az + 10° a, + 10° a, + 10° a, + 10° az + 10° az with a==7, a==30, a,=9, a==2

- A decimal number system is said to be of base or radix 10, because It was 10 digits and weatherients are multiplied by powers of 10.

- The binary number gutern is a different number gutern.

- The coefficients of the binary number given have only two possible values: o and 1

- Each coefficient as is multiplied by a power of the radix, of 2 and the sneults are added to obtain the decimal equivalent of number.

Eq: Binary number 11010:11 & equivalent to decimal number 26.75

1x24+1x2+0x2+1x2+0x2+2x1+22x1 = 26.75 16+8+2+0.5+0.25

- There are different number systems. In general, a number expressed in base - & system has coefficients multiplied by power of r.

an. 8 + and 17 + and 1 + ... + a, 7 + a, 8 + a, 8 + ...

man almin - the coefficients as range in values from a to 7-1.

Eq: bak-5 number

(4021.2) = 4x5 + 0x5 + 2x5 + 1x5 + 2x5 + 125xy 15 500 + 10 + 1 + 0.4

The coefficient values for box 5 can be only 0,1,2,3,4 - The octal number geten is a baje-8 system that has 8 digits: 0,1,2,3,4,5,6,7.

5: (127.84)8 = 188+288+7×80 + 4×85 - 64+16+,7+0.5 = (87.5)

Note: The digits 8 and 9 can't appear in a octal number.

- It is customary to bottom the needed or digits don the coefficients from the decimal system when the boxe of the number is less than 10.

- The letters so the alphabet one used to supplement the 10 decimal digits when the base of the number is greater than 10.

· Copple apach a newly of a in piles. for eq. En the hexadecimal (base-16) number eyetem,

The first 10 digits one boomsed from the decimal system. The letter A, B, C, D, E and f one used for the digits 10, 11, 12, 13, 14 and 15

Eq: A Hexadecimal number

(B65F)16 = 11×163+6×162+5×16+15×16°

= (46,687)10

The hexadecimal system is used to suppresent long strings of bits in the addresses, instructions, and duta in digital gutans. B65F is used to supresent : hospillo 0110 0101 1111

The conversion from binary to decimal can be obtained by adding only the numbers with powers of two corresponding to the bits that are equal to 1.

For Eq:  $(110101)_2 = 32 + 16 + 4 + 1 = (53)_{10}$

- In computer work

$2^{10} = K \text{ (Hild)} = 10^3 \quad 2^{20} = M \text{ (mega)} = 10^6 \quad 2^{30} = G \text{ (giga)} = 10^9$   $2^{40} = T \text{ (Tera)} = 10^{12} \quad 2^{50} = P \text{ (Peta)} = 10^{15} \quad 2^{50} = X = 10^{18}$

the number of his them to

- Computer capacity is usually given in bytes.

- A byte is equal to eight bits and can prepresents the ade of one keyboard character.

- A computer hard disk with 4 G1B ob storage has a capacity of  $4Gr = 2^2 \cdot 2^2 = 2^{32} = Capproximately 4 billian bytes)$

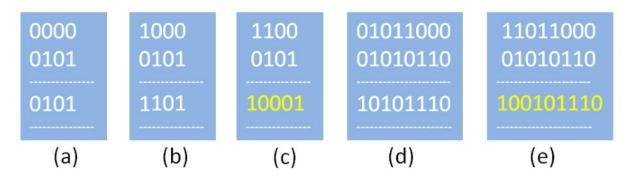

- Arithmetic operations with binary numbers in box or tollow the same rules as for decimal numbers.

Eq: addition, substraction and multipliplication of two binary numbers as tollows.

Augend 101101. minuend: 101101 multiplicand: 1011

Addend + 100111, substrational:-100111 multiplier: 101

1010100 101010

- Addition:

The own of two binary numbers is calculated by the same realisticant as in decimal except that the digits to seem in any significant preition can be only o or 1.

- Any carry obtained in a given significant position is used by the pair of digits one cignificant position higher.

#### substraction:

- Substraction is more complicated.

- The ruley are still the same of in decimal, except that the borrow in a given significant position adds 2 to a minuered digit.

- A boow in the decimal system adds to to a minueral digity Multiplication!

- Multiplication is simple.

- The multiplier digits are always I or o.

- Theretore, the partial products one equal either to a shitted copy of multiplicand or to 0.

### Number - Base Convenions

- -Representation of numbers in a different madix are said to be equivalent it they have same decimal suppresentation.

- for eq: (0011) and (001), are equivalent, both have same decimal value. 9.

- The conversion of a number in base-r to decimal is done by expanding the number in a power series and adding all the numbers

A down 1 tolon

and accumulating the enemainders.

Eq: convert decimal 41 to binary

$$2 \frac{41}{20 - 1}$$

$2 \frac{10 - 0}{25 - 0}$

$2 \frac{5 - 0}{1 - 0}$

Eq: Convert decimal (153) to octal (1,1)8

of ve Lorchapthon of the

Eq! Convert (41; to octal

Eg: Convort (0.6875), to binary

Eq:

$$(0.518)_{10}$$

to octal

(0.513)  $\times 8 = 4.104$

0.104  $\times 8 = 0.832$

0.832  $\times 8 = 6.656$

0.656  $\times 8 = 5.248$

0.248  $\times 8 = 1.984$

(0.513)<sub>10</sub> = (0.40651...)<sub>8</sub>

$$-\frac{1}{2} - \frac{(41.6875)}{(153.513)}_{10} = \frac{(101001.1011)}{2}$$

$$-\frac{1}{2} - \frac{(153.513)}{80} = \frac{(231.406517)}{8}$$

# octal and Hexadecimal Numbers

- The conversions from and to binary, octal and hexadecimal plays an important role in digital computer, because shaler pattern of hex charactery one easier to necognite than long patterns of o's 4 is - since ≥0 ≥2=8 4 ≥4=16, each octal digit corresponds to three binary digits and each hexadecimal digit corresponds to four binary digits ⇒ The first 16 numbers in the decimal, binary, octal thexadecimal as

| Decimal  | Binary   | octal       | Hexadecimal |

|----------|----------|-------------|-------------|

| (bak 10) | (base 2) | (bak 8)     | (baje 16)   |

| 0        | 0000     | 00          | 2 3         |

| 2 3      | 0100     | 03          | 4 5         |

| 6 1      | 0101     | 06          | m /sacc not |

| 7 11     | 01161    | TIME OF THE | 8           |

| 8        | 1000     | 10          | 9           |

- The conversion from binary to octal is accomplished by Partitioning the binary number into group of three digits each, starting from the binary point and proceeding to the littered to the right.

- The corresponding actal digit is assigned to each grap.

- E9: (10 110 001 101 011. 111 100 000 110)

- =) (26153.7406)<sub>8</sub>

- Conversion from binary to hoxadecimal is similar, except that the binary number is divided into groups of four digits.

- (2 C 6 B. F 0 6),6

- Enversion from octal (or) hexadecimal to binary is done by supresenting the each octal digit to its three-digit binary equivalent.

- similarly, each hexadecimal digit is converted to its town-digit binary equivalent.

$(673.124)_{8} = (10 111 011.001 010 100)_{2}$   $(306.0)_{16} = (0011 0000 0110.1101)_{2}$

### Compliments St Numbers:

- Compliments are used in digital computers to simplify the substraction operation and too logic operation.

- simplifying operations leads to simpler, less expensive circuits to implement the operations.

There are two types of complements for each base- & system.

- 1. Radix Complement (7's complement)

- 2. Diminished Rodex Complement. ((1-1)'s complement)

- The two types netword to as the e's' complement and is complement for binary numbers of 10's complement and 9's complement too decimal numbers.

# Diminished Radix Complement:

Given a number N in base r having n digits

The (8-1)'s complement of N is (8n-1)-N

for decimal number: 8=10 r-1=9So, (Diminished Rodix Complement) 9's complement of N is  $(0^{n}-1)-N$

planting 189 (2. it man = 4) (1) 7

(104-1)-N => 9999-N

-: 9's complement to a decimal number is obtained by substracting

of oring the est

The 9's complement 8t 547600 is

999999-547600 => 452399

The 9's complement of 012398 & 987601

the state of the first of the same of the same

For binary numbers Y=2 Y=1=1I's complement of  $N \neq (2^n-1)-N$ if N=4  $2^n=2^n=(10000)_2$   $4^n=(1111)_2$ i's complement of  $N \neq (2^n-1)-N$  = (1111)-N

Thus, the is complement of binary number is dotained by substracting each digit from 1.

we can have either 1-0=1(a) 1-1=0

is complement of 1011000 y 0100111

i's complement of 0101101 is 1010010 in the i's complement of a binary number is formed by changing is to 0's and 0's to 1's.

- (8-1)'s complement of octal or hexadecimal number is obtained by substracting each digit from 7 (a) F (decimal is), respectively

Rodox Complement

The 8's amplement 8t an n-digit number N in base r is defined as  $8^{\circ}-M$  for N \$0 \$ as a for N=0.

For decimal r=10

Annalysis Also is re-

$y_0 - M \Rightarrow \omega_0 - M$

: 10's complement st N can be termed by Leaving all least significant o's unchanged, substracting the tisut non zero least significant digit from 10, and substracting all higher digits from a They

10's complement of 012398 4 987.602

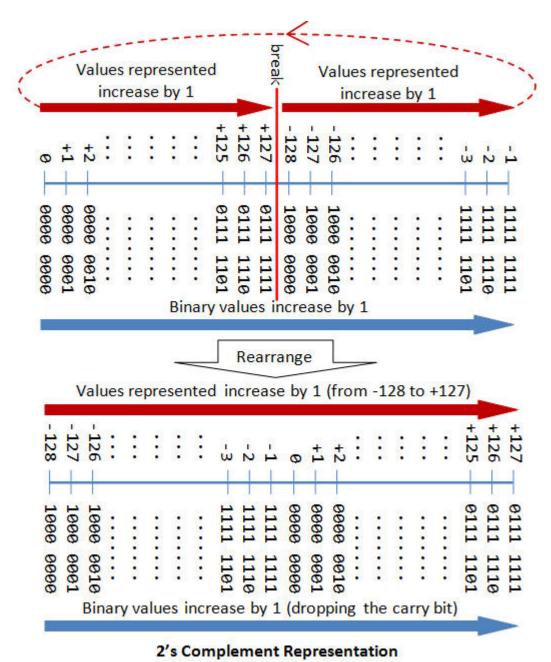

Similarly 2's complement of N can be tormed by leaving all least significant o's and the tiset I undranged and supplacing i's with o's and o's with i's in all other higher significant digits.

2's complement of 1101100 & 0010100 e's complement of 0110111 & 100 1001

- It the original number N contains the radix point, the point should be snemoved temporarily in order to form the r's 4(r-1)'s complement.

- complement.

The godix point is then nestored to the complemented number.

- The complement of the complement mentures the number to its

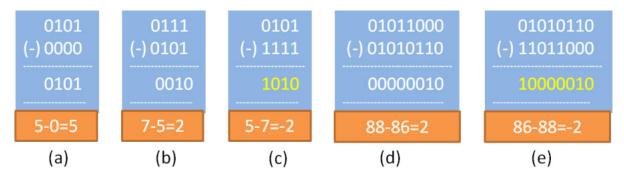

Substraction with complements

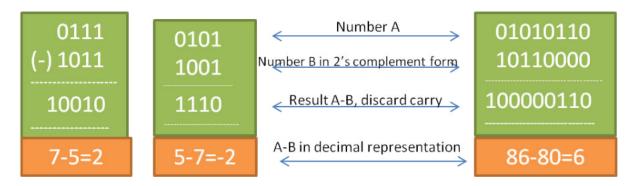

unsigned The aubstraction of two n-digit numbers M-N in bage of can be done as follows.

- 1. hold the minued 14 to the r's complement of the substrachend, Mathematically  $M + (r^2 - H) = M - N + 8'$

- 2. It M > N, the sum will produce an end away r, which on be dynaded; what left is the result 19-N.

- 3. It MICH, the sum does not produce and only and y equal to r'-(N-M), which is is complement of (N-M). . To obtain the answer in a tramiliar term, take the r's complement so sun & place a regative sign in tront.

Eg: wing 10's complement, substract 72532-3250

M = 72532

10's complement &N = 96750

Sun = 169282

Discord end any 105 = 100000 69285

59: using 10's complement, substract 3250 - 72532

M : 03250

10's complement of N = 27468 30718 they

Eq: Given the two binary numbers x=1010100 & y=1000011, perform substraction as x-y 4 b) & y-x by wing 2's complement

2's completed y = 0 11111.01

Discord end awyst: 10000000

D) 7= 1000011

2's complement & x = 01011.00

There is no ord away y-x=-(2') complement of 1101111)

= \_000001

#### Examply to work:

1) Convert the tollowing to decimal and then binary

a) (1876),6 b) (AB22),6 c) (1212), d) (1556),

2) anvert the tollowing hexa decimal numbers into an equivalent binary numbers

(i) 58 (ii) 234 (iii) ABC (iv) FB18

3) Substract the tollowing decimal numbers using 9's complent

(i) 347-265 (ii) 49-84 (iii) 349-436 (iv) 9-4

- 4) Convert the trollowing to octal and Hetadecimal

- is the state of the part of the state of the state of a) 100 101101011 b) 10 1101000001012

- c) 791,0 d) 1600,0 e) 197,0

Eg: using is complement

I The state of the State of the

9 x= 1010100

is complement of y: 0111100

Sum = 10 010000

End-around carry:+

00 1 000 1

b) y-x= 1000001- 1010100

7:1000011

There is no end-coory. .: Y= x= - (is complete of 1101110) the talkers have derived and it are required in

- In \$ (8-1)'s amplement enemoving the end around avoing and to the sum is sufferred to as an end-around avery

- The procedure with end-orand coory is also applicable to

### Signed Binary Mumber:

- Possitive integers (including zero) can be represented as unsigned nois.

- In ordinary arithmetic, a negative no is indicated by minus sign and a positive number by a plus sign.

- Because of hardware limitations, computers must represent everything with binary digits.

- in the lebt most position ob the number.

- The convention is to make the eign bit o for positive f

- Both signed and unsigned binary numbers consults of a string of bits when suppresented in a computer.

- The user determines whether the number is signed or not

- It the binary number 4 signed, then the lebt mat bit represents the sign and the riest of the bits represent number.

- It the binary number is unsigned, then the left most bit it the most significant bit of the number.

- Eq: the string of bits 01001 is considered as

9 unsigned number

+ 9 signed number.

- the string of bits 11001 is considered as

25 unsigned number

-9 Signed number.

a symbol (+ or -) or a bit (o or 1) indicating the sign.

Signed Complement System

when arithmetic operations are implemented in a computer, it is more constraint to use a different system, substrated to as the signed complement system, for supresenting negative numbers.

In this system a negative number is indicated by its complement whereas the signed magnitude system negates a number by changing its sign, the signed complement system negates a number by taking its complement.

Eq: Consider the number q, suppresented in binary with eight bit

Birray equivalent of +9 is 00001001 there are 3 ways to suppresent -9

Signed magnitude representation 10001001

Signed is complement representation 11110110

Signed 2's complement representation 1111021

Representation st signed numbery using 2's on is complement method.

1. It the number is possitive, the magnitude is nepresented in its true binary term and a sign bit o is placed in trent to the most 1958.

| Table ! |        |         |

|---------|--------|---------|

| Signed  | Birary | Numbery |

| Decimal   | signed - 2's<br>complement | signed-1's amplement | signed magnitude | 1     |

|-----------|----------------------------|----------------------|------------------|-------|

| 47        | 0111                       | 0 111                | 0000111          | 4     |

|           | 0110                       | 0110                 | 0110             |       |

| +6        | 0 101                      | 0101                 | 0101             | 1,.   |

| +5        |                            | 0100                 | 0 100            |       |

| +4        | 0100                       | 0011                 | 0011             |       |

| +2        | 0010                       | 0010                 | 0010             |       |

| +1        | 10001                      | 0001                 | 0 00 1           |       |

| +0        | 0000                       | 0000                 | 0 000            |       |

|           | -                          | 1 1 1 1              | 1000             |       |

| 20 = 1    | 11101                      | 10110                | 1001             |       |

| 1 52      | - AV - To                  | 1101                 | 1010             |       |

| -3        | 214/1021                   | 1100                 | the 1011 1       | or i- |

| -H-Marile | 1100                       | 1011                 | 1100             |       |

| -5        | 1011                       | 1010                 | 1.1010 m         |       |

| -6        | 1010                       | 1110                 | 1110             |       |

| -7        | 1001                       | 1000                 | and a little     |       |

| -8        | 1000                       | £ —                  | -                |       |

special case in e's complement! whenever a signed number has a 1 in the sign bit and all or for magnitude bits, the decimal equivalent is -e? sign bit and all or for magnitude bits, the decimal equivalent is -2°.

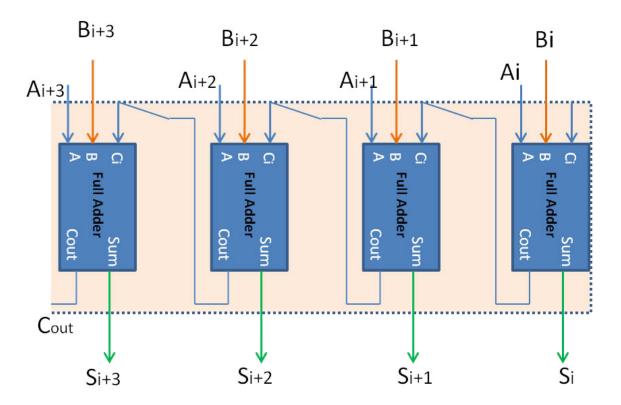

Arithmetic Addition

The addition of two signed binary numbery with negative numbery suppresented in signed - e's - complement form is obtained from the addition of the two numbers, including their sign bits.

A coory out of the sign-bit position is discorded.

+6 00000110 00001101 00010011

+6 00000110 -13 11110091

11111010 1 1100000T T

1111010 -13 11110011

carry has to be

hay to be

discorded.

# Arithmetic Substraction

- Substraction of two signed binary numbers when negative numbers are in e's complement from is simple and can be stated as Adlaws.

Take the e's complement of the substrational Cincluding the sign bit) and add it to the minuend (including the sign bit) A carry out of the sign-bit position is discarded.

This procedure is adopted because a substraction operation can be changed to an addition operation it the sign of the substratand is changed, as is demonstrated by the tollowing robationship.

$$(\pm A) - (\pm B) = (\pm A) + (-B)$$

$(\pm A) - (-B) = (\pm A) + (\pm B)$

Eq! (-6)-(-13)=+7

Mad 1 1 1 1 1 0 10 - 11110011

11111010 000001101 700000111 away has to be discarded.

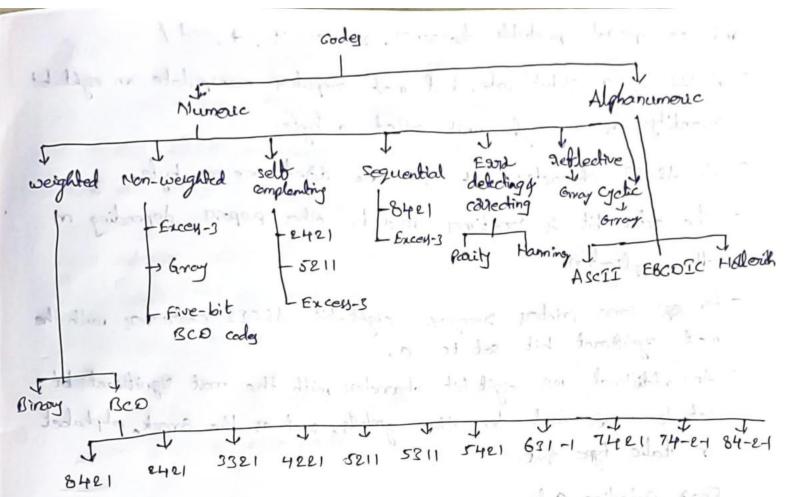

### Binary Codes

- A n-bit binary ande is a group of n-bits that can have upto en distinct combinations of o's and 1's.

- Each combination represents one element of the set that is being coded.

- A set of 4 elements can be raded with two bits, with each element assigned one of the bit combinations: 00,01,10,11.

- A set ob 8 elements sieguires a three bit cade and a set ob

- The bit combination of an n-bit cade is determined from the count in binary from 0 to  $2^n-1$ .

- Each element must be assigned a unique binary bit ambination, and no two elements can have the same value; otherwise the code assignment will be ambiguous.

- The minimum number of bits prequired to cade 2° diffinct quantities is no there is no maximum number of bits that prequired to code of may be used for a binary ande.

# Binary-Coded Decimal Code:

- A BCD code is one, in which the digits so a decimal number are encoded one at a time into groups so trown binary digits.

- There codes combine the treatures of decimal and binary numbers.

- In order to suppresent decimal digits 0,1,2,...,9, it 4

- such a sequence of binary digits which suppresents a decimal digit is called a code wad.

- A binary code will have some unaugned bit combinations it the number of elements in the set is not a multiple power of e.

- The 10 decimal digits from such a set.

- A binary code that distinguishes among to elements must contain at least four bits, but 6 out 86 16 possible combinations remain un-agged kugered.

- This schome is called Binary Goded Decimal and is commonly netroned to as BCD.

the tollowing table gives the tour-bit code for one decimal doit A number with K bits decimal digits will require 4k bits in

otiful, and

#### Binary Coded Decimal (BCD)

dried mile

| Dec          | imal symbol | BCD Digit |

|--------------|-------------|-----------|

| James J.     | do L        | 0000      |

|              | Line to the | 0001      |

|              | 2           | 0010      |

|              | 3           | 0011      |

| provide Land | 4. 1 80 00  | 0100      |

|              | 5           | 0101      |

| The same     | 6           | 0110      |

|              | 7           | 0111      |

|              | 8           | 1000      |

|              | 9           | 1001      |

- the binary combinations 1010 through 1111 are not used and have no meaning in RCD.

Eq: consider decimal (185), 4 its corresponding value in BCD & birary

(185),0 = (0001 1000 0101) BCD = (10111001)2

### BCD Addition:

- Consider the addition of two decimal digits in BCD, together with a possible carry from a previous less significant pair of digits.

- since each digit does not exceed 9, sum cannot be greater than  $9+9+1=19, \quad \text{with 1 being a previous corry.}$

- Suppose we add the BCD digits as it they were binary numbers.

- Then the binary wern will produce a signific in the range trom o to 19.

- In binary, this stange will be trom occo to 100.11. But in RCD, it is trom occo to 1 1001, with the birut 1 being a carry and the next trour bily being the BCD Rum.

- when the birary rum is equal to a less than 1001 (without covery), the corresponding BCD digit is correct.

- when the binary rum is greater than a equal to 1010,

the small is an invalid BCD digit.

- The addition sto 6 = (0110) to the binary cum (11-1)

converts it to the correct digit and also produces a carry of nequired.

- This because a more in the most significant bit position and

Consider the tollowing BCD additions.

The addition to two n-digit unsigned BCD numbers tollows the same procedure

consider

$$184+576=760$$

in BCD

BCD  $0001 1000 0100 184$

$0101 0111 0110 +576$

$0110 0110 0110$

$0110 0110$

$0110 0110$

# BCD Substraction

- The BCD substraction is performed by substracting the digits to each 4-bit group of the substrated trom the corresponding 4-bit group of the minuend in binary starting from the LSD.

- It there is no bottom from the next higher group then no correction is enequived.

CThy is done to skip 6 illegal states)

# other Decimal codes

4 de Jujos I a

- Binary codes for decimal digits enequire a minimum of town bits

- Many sown different rodes can be termulated by avianging four bits into 10 distinct combinations.

- Each code vers only 10 out of a possible 16. bit combinations that can be accoranged with town bits

- The other six unused combinations have no meaning and should be avoided.

- BCD and the 2421 code one examples of weighted rodes.

- In a weighted code, each bit position is assigned a weighting tactor in such a way that each digit can be evaluated by adding the weights of all the is in the coded combination.

#### M.JOSHNA

- The bit assignment 0110, for eq: is interpreted by weights to suppresent decimal 6. because 8x0+4x1+2x1+0x1=6.

- Note that some digits can be coded in two possible ways in 2421 code.

- for invarie, decimal 4 can be coded to bit combination 0100 as 1010, since both combinations add upto a total weight of 4.

Table: Some different Binary Codes for decimal digits.

| Decimal<br>Digit | BCD<br>8421 | 2421  | Exces-3 | 8,4,-2,-1 |

|------------------|-------------|-------|---------|-----------|

| 0                | 0000        | 0000  | 0011    | 00 00     |

| 1                | 0001        | 0001  | 0100    | 0111      |

| 2                | 0010        | 0010  | 0101    | 0110      |

| 3                | 0011        | 0011  | 0110    | 0101      |

| 4                | 0100        | 01.00 | 0111    | 0100      |

| 5                | 0.101       | 1011  | 1000    | 1011      |

| 6                | 0110        | 1,100 | 1001    | 1010      |

| 7                | 0 111       | 1101  | 1010    | 1001      |

| 8                | 1000        | 1110  | 1011    | 1000      |

| 9                | 1001        | 1111  | 1100    | 5. (II.)  |

| nund             | 1010        | 0101  | 0000    | 000 1     |

| codes            | 1011        | 0110  | 0001    | 0010      |

| codes            | 1100        | ou    | 0000    | 001)      |

| 4 phones         |             | 1000  | 1101    | 1100      |

|                  | 1101        | 1001  | 1110    | 1101      |

|                  | 1110        | 1010  | 1111    | 1110      |

- 2421 and the excess-3 are examples of self-complementing codes.

- such codes have the property that the 9's complement to a decimal number is obtained directly by changing is to o's and o's to i's

Eq: Decimal 395 excess-3 2421

9's compt of 395 y 604 1009 0011 0111 1000 0000 0100

- The excess-s code has been used in some older computers because of its self-complementing property.

- Excers-3 is an unweighted code in which each coded combination is obtained from the corresponding binary value plus 3.

- The 8,4,-2,-1 code is an example of anigning both positive and negative weights to a decimal code.

# Gray Code:

- the output data ob many physical systems are quantities that are continuous.

- These data must be converted into digital form before they are applied to a digital systems.

- Continuous con analog intermedian is converted into digital form by means so analog-to-digital converter.

- The advantage of Gray Code over the draight binary numbers sequence is that only one bit in the code group changes in going brom one number to the next number.

- Eq: in going from 7 to 8, the gray code changy from 0100 to 1100.

only fight bit changy from 0 to 1; then three bits memain same.

By contrast, with binary numbery the change from 7 to 8 will

- the Gray rade is a non-weighted rade, and is not suitable for arithmetic operations.

- An N-bit Gray code can be obtained by retriecting an N-1 bit code about an axis at the end of the code, and pulling the MSB of a above the axis and the MSB of 1 below the axis.

Retriection of Gray-Codes is shown in tollowing table.

|             | Gray    | Code     | e         |       | . 1-1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             | Decim | al     | 4-bit binou |

|-------------|---------|----------|-----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|--------|-------------|

| 1-bit       | 2       | -bit     | 3-bit     | · ak  | 4-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | net<br>Sett |       | . F    | 1-11        |

| 0           |         | 0        | 000       | Price |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -, 41       | K     | 1-01-1 | 0000        |

| has gotting | 0       | propo    | 001       |       | 0 001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             | N8    | ri a   | 0000        |

|             | - 1     | -1       | 011       |       | the state of the s | . 1         | 4     | n 100  | 0100        |

|             | 1       | 0        | 010       |       | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             | 5     |        | 0101        |

| ro fall o   |         |          | 1 10      |       | 0101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Hz          | 7     | 1 1    | 0110        |

|             |         |          | 101       |       | 0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             | 8     |        | 1000        |

| pth m. h    | all or  | र्वेटी ल | 100       | 2.    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | ly sw | dala   | 1010        |

|             | X 1 1 1 |          |           |       | 1 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 100         | 9     |        |             |

|             | 0.33    |          | i Indyawa | 20 15 | 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             | III   |        | 1100        |

|             |         |          |           |       | 1710                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |       |        | 1101        |

| antic For   |         |          |           |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |       |        |             |

|             | W. H.   | Tallance | dod.      | note. | 1011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | K           | 25    | day to | 1111        |

| n et out    |         | herony   |           |       | 1001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ~           | 106   |        | 0.50        |

| of chemics  |         |          |           |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4:1         | 1 7   | WE .   |             |

|             |         |          |           |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -10         | 41-4  |        |             |

### ASCII character code

- Many applications of digital computors naquires the handling of not only of numbers, but also or other chanacters or symbols, such as letters or alphabets.

- An alphanumeric shoracter set is a set to elements that includes the so decimal digits, 26 letters of the alphabet, and a number to special characters.

- The standard binary code for the alphanumeric charactery if the American standard code for Information Enterchange (ASCII), which was seven bits to code 128 chanactery.

- The seven bits of the rade one designated by b, through by with by the most significant bit.

- The ascir code antains 94 graphic characters that can be printed of 34 non printing abaracters used for various control functions.

M.JOSHN*A*

and se special printable characters, such as 1. , + , and f

- ASCII is a 7-bit rade, but most computers manipulate an eight his quantity as a single unit called a byte.

- . ASCII character most often are stored one per byte.

- The cebra bit is sometimes used for other purposes, depending on the application.

- for eq: some printery necognize eight-bit ASCII characters with the most significant bit set to o.

- An additional 128 eight-bit characters with the most significant bit set to 1 are used for other symbols, such as the Greek. alphabet or italic type font.

### Earla - Detecting Code

- To detect oursy in data Communication and proceeding an eighth bit is sometimes added to the ASCII character to indicate its painty.

- A parity bit is an order bit included with a message to make the total number of is either oven (a) add.

Consider the trollawing two charactery and their even and odd parity.

ASCII = 1000001 01000001 11000001

ASCII = 1010100 11010100 01010100

- The parity bit is helpful in detecting words during the transmission of intermation from one location to another.

- This trunction is handled by generating an even parity bit at the sending end for each docacter.

- The eight bit charactery that include painty bits one bransmitted

- the parity of each character is checked at the overexing end.

- It the parity of the secreted character is not even, than at least one bit has changed value during the transmission.

- This method detects one, three, or any odd combination of exists in each character that is transmitted.

- An even combination to cooky, however, goes undetected, and additional and detection codes may be needed to take cone of that possibility.

- After delecting an expiratione parability is to sequent statement won of the message on the assumption that the cool was random and will not occur again.

- Thus, it the species a detects a parity early, it sends back the ASCIT NAK antrol character ansyting of an even-parity eight bits

- It no could is delected, the energial sends back an Ack control diaracter, namely, 00000110.

- Et, other a number of attempts, the transmission is still in early, a message can be sent to the operator to check for maltrunctions

# Kepresentation

Due to limitations of hardware, computers must suppresent everything with o's f's, including the aign of a number. As a consequence, it is customary to represent the agn bit pulsced in the lebb-most position to the number. The convention is to make the uga bit equal to o ter positive numbers 4 to 1 for negative numbers.

In addition to the ugn, a number may have a binary (or decimal) Point. The position of binary point is needed to supresent tractions, integers, (or) mixed integer-fraction numbers.

There are two ways or specitizing the position of the binary point in a siegiller.

- 2. Floating Point Representation.

- Fixed-Point Representation assumes that the binory point is fixed in one position.

The two positions most widely und are

- (i) a binary point in the extreme left of the negiter to make the World number a traction.

- (ii) a binary point in the extreme, right of the significan to make the stored number an integer.

- The floating-Point Supprepentation vy a record Suggister to 1880 a number that designates the parition of decimal point in the first negister.

# Floating-Point Representation

The floating point representation to a number has two Parts. The tirut part sepretents a agned, fixed point number called the mantissa. The second part designates the position of binory (or decimal) point and y called exponent. The fixed point mantissa may be a fraction (ar) an integra

12: Gossider the decimal number. + 6132.789

Floating point Depresentation 4

Fraction Exponent +0.6132789 +04

The value of the exponent indicates the actual position of the decimal point is town positions to the right of the indicated docimal point in the fraction.

Notation 4: +0.6132789 X 10

Floating-Point is always interpreted to supresent a number mxre in the tollawing form.

m - mantissa e - exponent (including their kign) and of all drawny - radies and and interest to the

Eg: Consider a binary number + 1001.11 is supresented with 8-bit traction & 6-bit exponent as tabus.

> Fraction Exponent 0 100/110 000100

: Floating point number is mx2=+(.1001110) x2

#### Normalization

A floating Point number is said to be normalited, it the most agniticant digit of the mantissa is non zero.

for eg: Desimal number 350 y normalized but 00035 y not. Moundized numbers provide the manumum possible precises

for the bloating point number v

Clandard forms st floating Point numbers

1. ANSI (Amoural National Standords Institute)

2. IEEE (Institute of Electrical & Electronic Engineery)

The ANSI 32-bit floating point numbery in byte format. is given below.

Byle 4 Byte format SEEE . HIMMMMMM MMMMMMM - MMMMMMMM Martissa

Binooy Point

S - Sign of Mantissa

E - Exponent bits in 2's complement 1' man ? 5000 47

- Mantiga bits.

I con sol - soll CHARZO

Eg:

= 0 0000 100 11010000 00000000 00000000

$$-17 = -10001 = -0.10001 \times 2^{5}$$

= 10000101 10001000 00000000 000000000

= 1111110 | 0000000 0 0000000 00000000

. Almer for minds

# or appear to a man and all all and to add the hard and REEE format

1. Single Precision 32-bits

| sign  | Exponent | Mantissa                           |

|-------|----------|------------------------------------|

| 1-Bit | S-Bih    | of production this product tide of |

$$= 1.010101001 \times 2^{6}$$

$$(2^{n+1})$$

Bland Exponent: 127+6=133=10000101

IEEE 754 single Precision Representation is

# 0 10000101 010101001000000000000000

Hexa decimal y

64-bit

|      | 6        | 4 bits - |

|------|----------|----------|

| xgn  | Exponent | Mantissa |

| -BIF | 11-64    | 52-bit   |

母:

(85.125) = 1.010101001 X26

Biand Exponent: 1023+6=1029=10000000101

singn bit : 0

SEEE 754 Double precision &

0 10000000101 010101001 0.....0 49 bits - pad zero

Hexa decimal value

4055480000000000

| M.JOSHNA |  |

|----------|--|

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

## **UNIT I-PART-II**

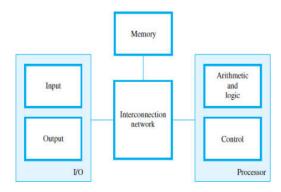

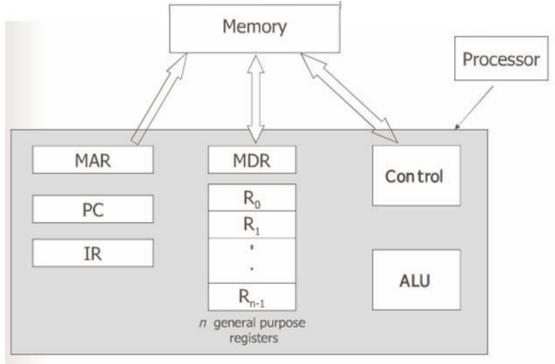

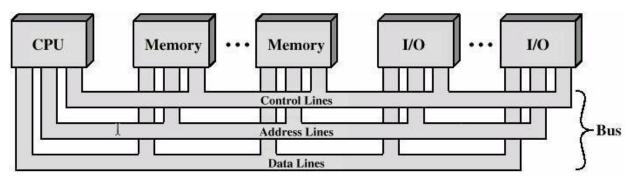

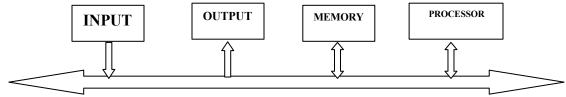

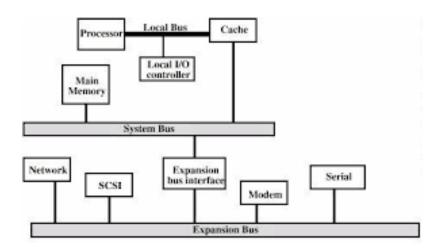

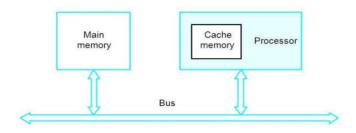

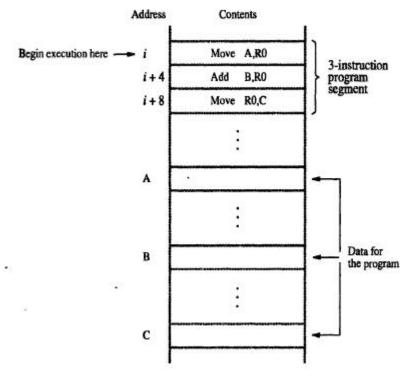

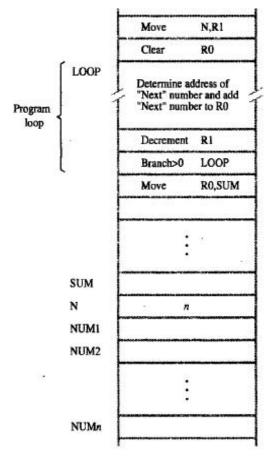

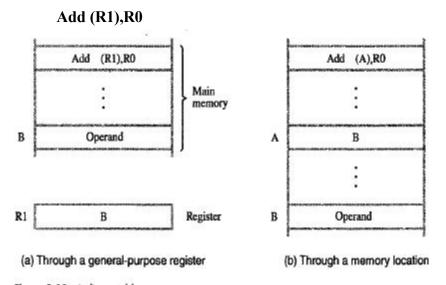

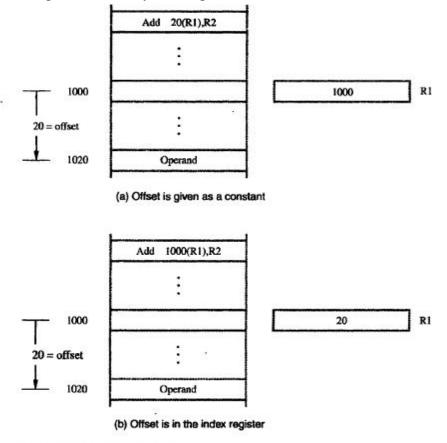

<u>Syllabus:</u> Basic Structure Of Computers: Functional unit, Basic Operational concepts, Bus structures, System Software, Performance, The history of computer development.

<u>Computer:</u> Computer is a fast electronic calculating machine that accepts digitized input information, processing it according to a list of internally stored instructions and produces the resulting output information. The list of instructions is called as a Computer program and the internal storage is called as Computer memory.

<u>Types of Languages:</u> Just as humans use language to communicate, and different regions have different languages, computers also have their own languages that are specific to them. Different kinds of languages have been developed to perform different types of work on the computer. Basically, languages can be divided into two categories according to how the computer understands them.

- 1. **Low-Level Languages:** A language that corresponds directly to a specific machine. Low-level computer languages are either machine codes or are very close them. A computer cannot understand instructions given to it in high-level languages or in English. It can only understand and execute instructions given in the form of machine language i.e. binary. There are two types of low-level languages:

- 1. Machine Language: a language that is directly interpreted into the hardware. Machine language is the lowest and most elementary level of programming language and was the first type of programming language to be developed. Machine language is basically the only language that a computer can understand and it is usually written in hex. It is represented inside the computer by a string of binary digits (bits) 0 and 1. The symbol 0 stands for the absence of an electric pulse and the 1 stands for the presence of an electric pulse. Since a computer is capable of recognizing electric signals, it understands machine language.

## **Advantages:**

Machine language makes fast and efficient use of the computer.

lt requires no translator to translate the code. It is directly understood by the computer.

## **Disadvantages:**

All operation codes have to be remembered

All memory addresses have to be remembered.

It is hard to amend or find errors in a program written in the machine language.

2. Assembly Language: A slightly more user-friendly language that directly corresponds to machine language. Assembly language was developed to overcome some of the many inconveniences of machine language. This is another low-level but very important language in which operation codes and operands are given in the form of alphanumeric symbols instead of 0's and 1's.

These alphanumeric symbols are known as mnemonic codes and can combine in a maximum of five-letter combinations e.g. ADD for addition, SUB for subtraction, START, LABEL etc. Because of this feature, assembly language is also known as 'Symbolic Programming Language.'

## **Advantages:**

Assembly language is easier to understand and use as compared to machine language.

lt is easy to locate and correct errors.

It is easily modified.

## **Disadvantages:**

- Like machine language, it is also machine dependent/specific.

- Since it is machine dependent, the programmer also needs to understand the hardware.

- 2. **High-Level Languages:** Any language that is independent of the machine. High-level computer languages use formats that are similar to English. The purpose of developing high-level languages was to enable people to write programs easily, in their own native language environment (English).

High-level languages are basically symbolic languages that use English words and/or mathematical symbols rather than mnemonic codes. Each instruction in the high-level language is translated into many machine language instructions that the computer can understand.

## **Advantages:**

- 1. High-level languages are user-friendly

- 2. They are easier to learn.

- 3. They are easier to maintain

- 4. A program written in a high-level language can be translated into many machine languages and can run on any computer

- 5.programs developed in a high-level language can be run on any computer text

## **Disadvantages:**

6. A high-level language has to be translated into the machine language by a translator, which takes up time

<u>Computer Types:</u> Basing capacity, technology used and performance of computer, they are classified into two types

- → According to computational ability

- → According to generation

#### According to computational ability (Based on Size, cost and performance):

There are mainly 4 types of computers. These include:

- 1.Micro computers

- 2. Mainframe computers

- 3. Mini computers

- 4. Super computer

#### 1. Micro computers: -

Micro computers are the most common type of computers in existence today, whether at work in school or on the desk at home. These computers include:

- 1. Desktop computer

- 2. Personal digital assistants (more commonly known as PDA's)